- Information

- AI Chat

Was this document helpful?

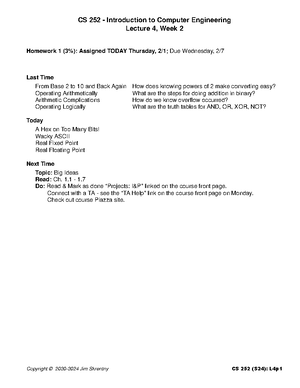

ECE252 Exam 2 - Study guide for Exam 2.

Course: Introduction To Computer Engineering (COMP SCI/E C E 252)

18 Documents

Students shared 18 documents in this course

University: University of Wisconsin-Madison

Was this document helpful?

electronic switches --- switches controlled electronically instead of by

mechanical action, the foundation upon which all modern computers are built

switch open --- light off, open/ broken circuit, powers voltage cannot push

electrons through the bulb

switch closed --- on, complete circuit, powers voltage can push electrons

through the bulb

transistors --- electronic switches made of semiconductor materials

MOS --- metal oxide semiconductor

voltage --- transistors use at their "gate" to open or close the switch

N-type --- +V at gate closes the switch, negative side electron switch, pulls out

down to 0V

P-type --- 0V at gate closes the switch, positive side electron switch, pulls out

up to +V

CMOS --- complementary MOS

CMOS logic gates --- N-type and P-type MOS transistors are used

Not Gate CMOS ---

not gate logic ---

NOR gate CMOS ---

OR gate CMOS --- NOR gate notted

serial connection (NOR) --- on top both inputs must be a 0 to pull c up to 1

parallel connection (NOR) --- on bottom only on input must be 1 to pull c down

to 0